|

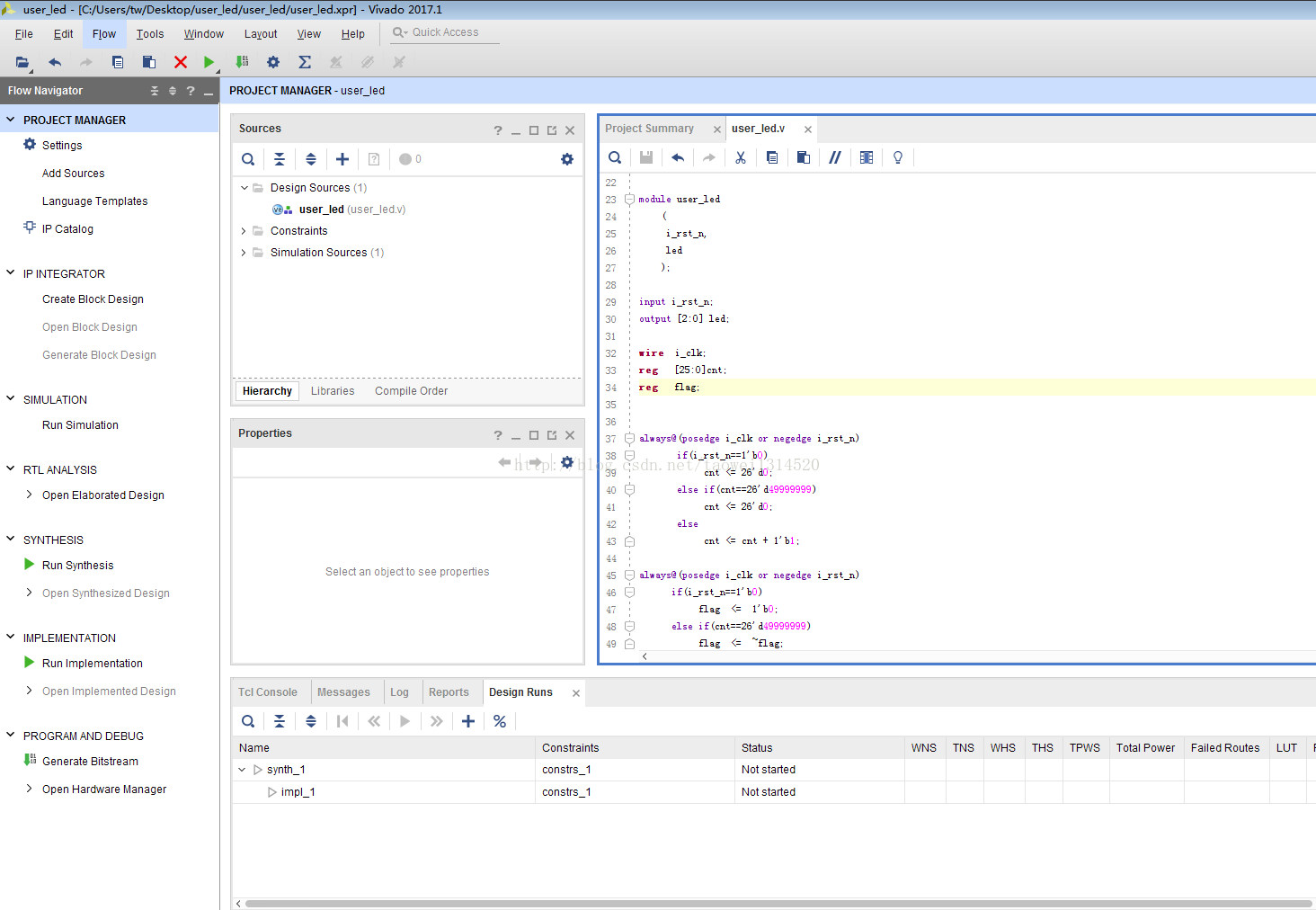

原文连接:https://blog.csdn.net/taowei1314520/article/details/77939396 有修改。 背景: FPGA新手,学习时使用的是PS和PL分别配置晶振的开发板,实际项目中使用的只有PS配晶振的核心板。测试外围电路并不需要很复杂的程序,不需要PS加载系统,修改流水灯程序IO口输出即可。经过查询,可以利用PS输出时钟驱动PL。 Step1 这里是已经新建好的FPGA流水灯如下图所示:  程序为:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2017/08/28 17:53:04

// Design Name:

// Module Name: user_led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module user_led

(

i_rst_n,

led

);

input i_rst_n;

output [2:0] led;

wire i_clk;

reg [25:0]cnt;

reg flag;

design_1_wrapper u1 //将PS部分50M的时钟例化到PL中

(

.FCLK_CLK0(i_clk)

);

always@(posedge i_clk or negedge i_rst_n)

if(i_rst_n==1'b0)

cnt <= 26'd0;

else if(cnt==26'd49999999)

cnt <= 26'd0;

else

cnt <= cnt + 1'b1;

always@(posedge i_clk or negedge i_rst_n)

if(i_rst_n==1'b0)

flag <= 1'b0;

else if(cnt==26'd49999999)

flag <= ~flag;

assign led[0] = flag;

assign led[1] = flag;

assign led[2] = flag;

endmodule

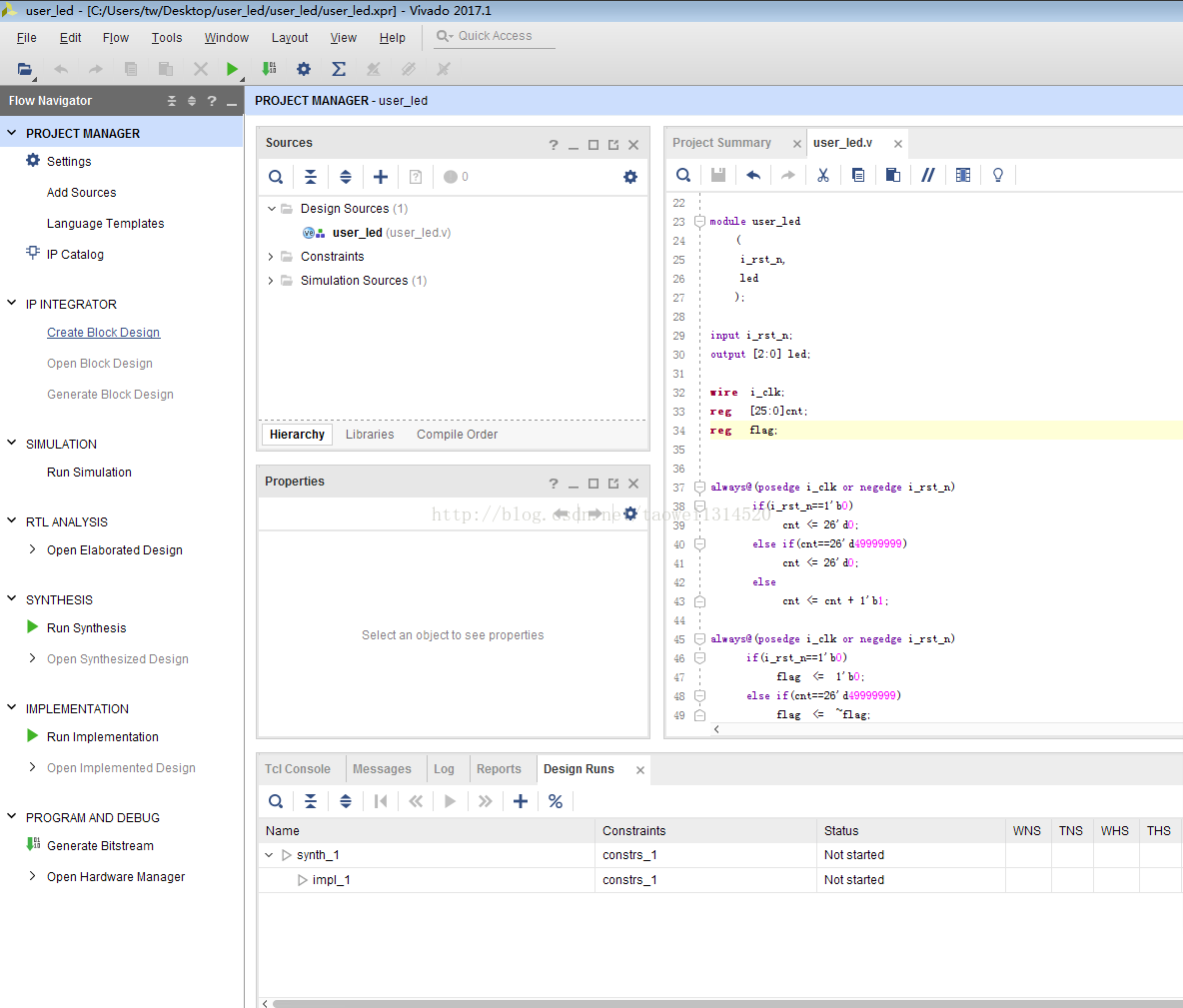

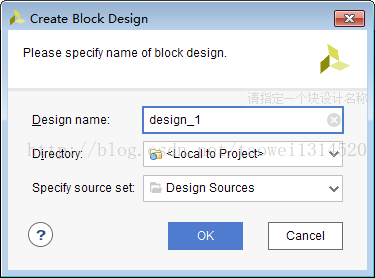

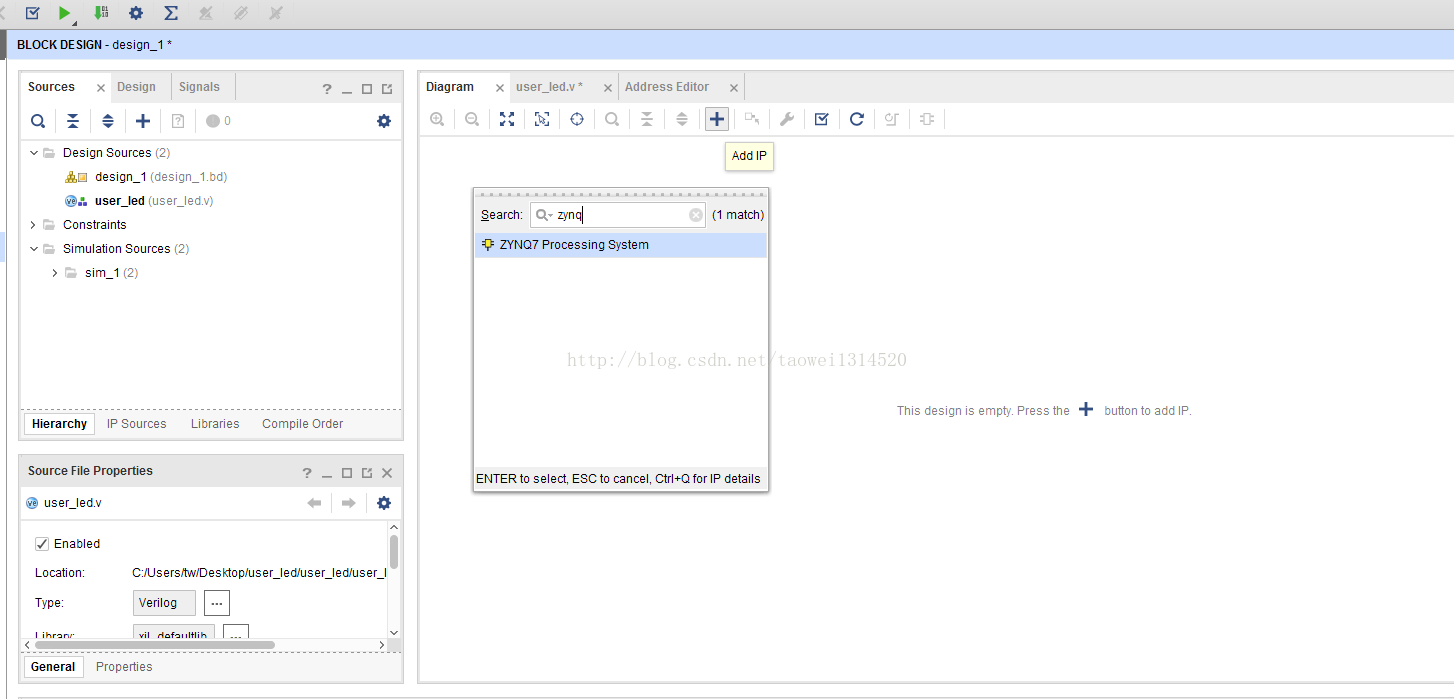

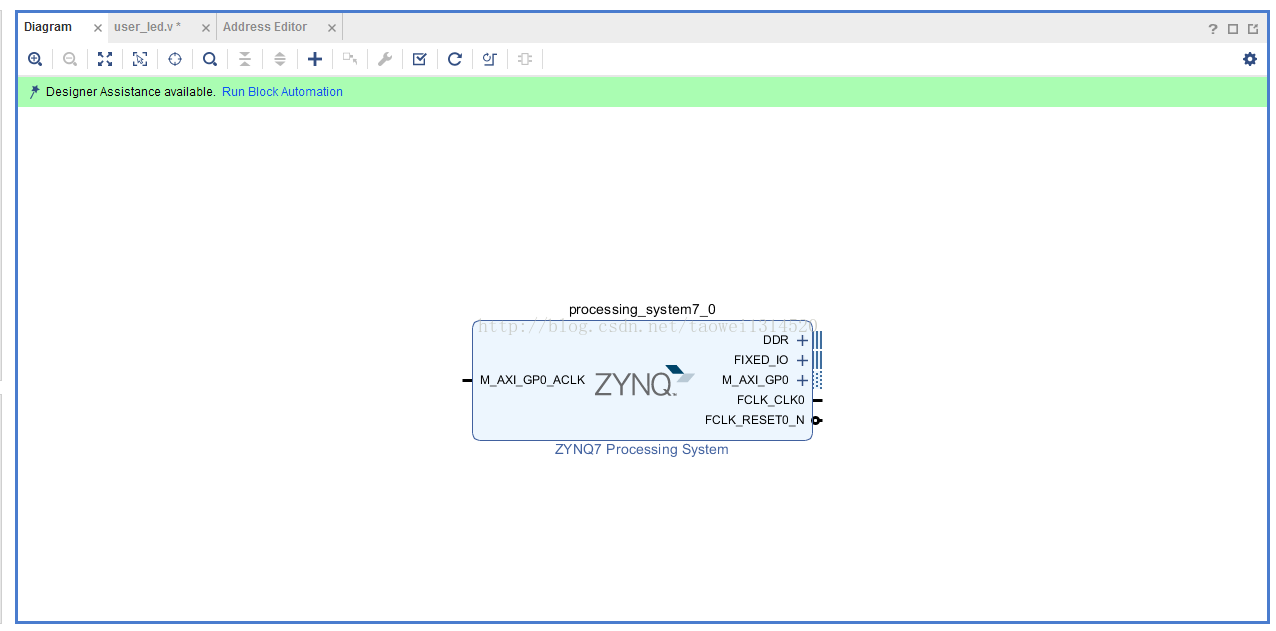

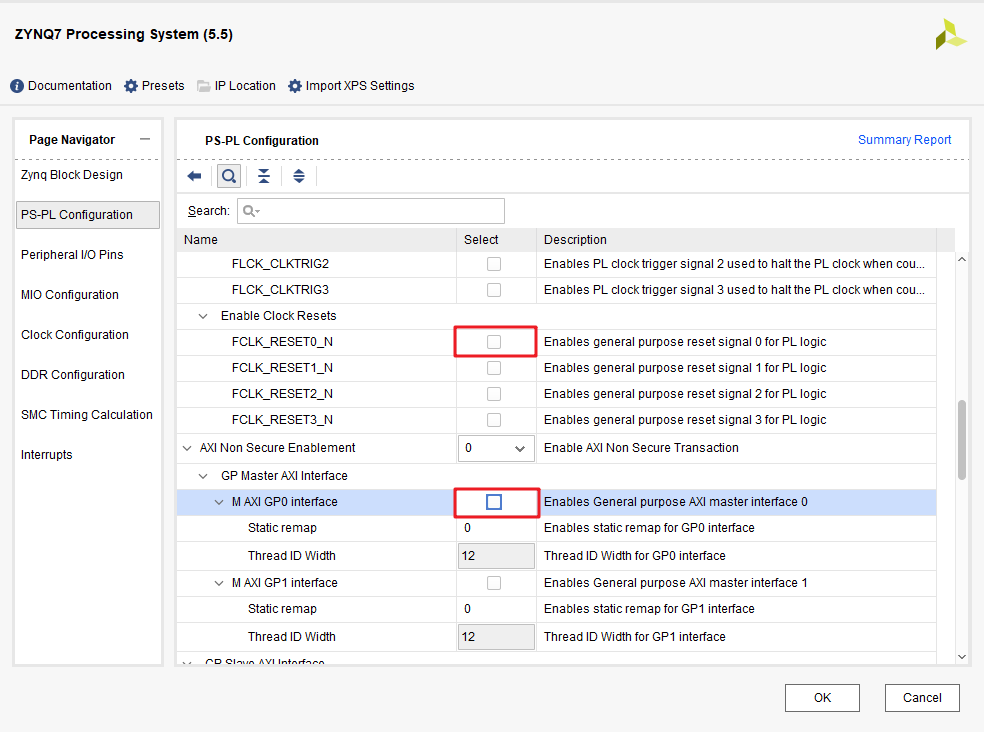

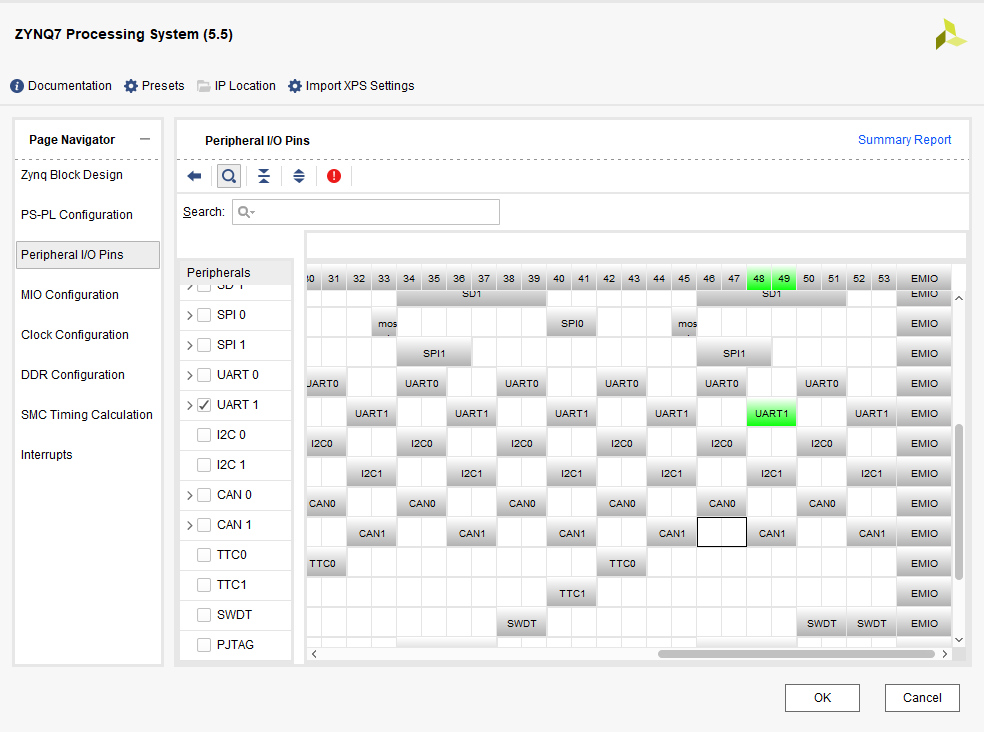

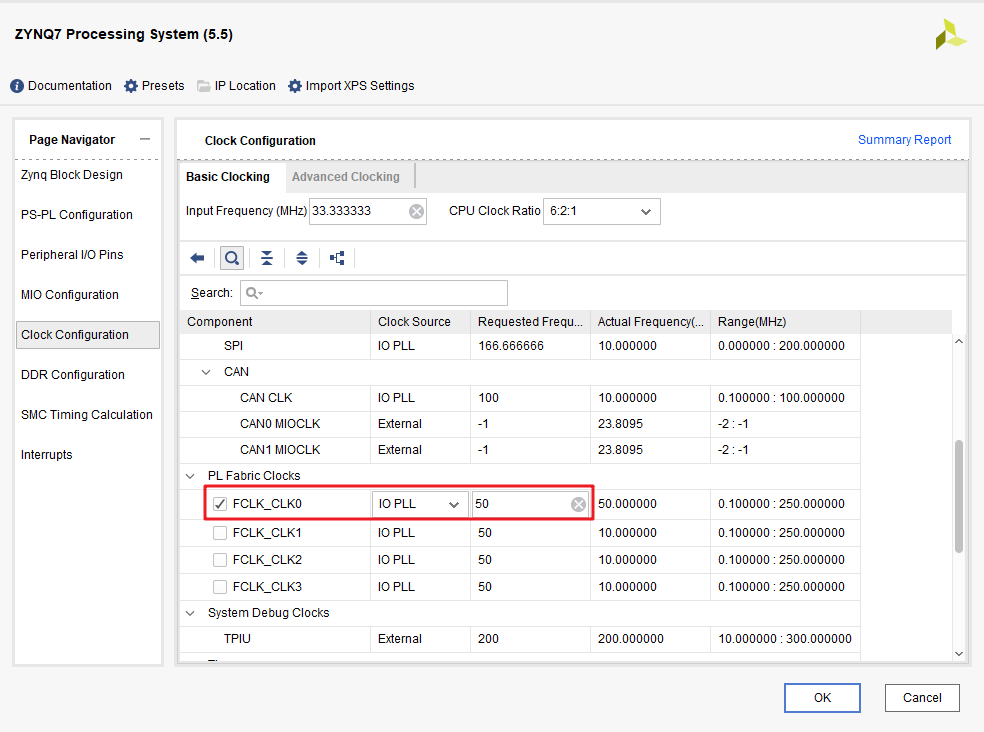

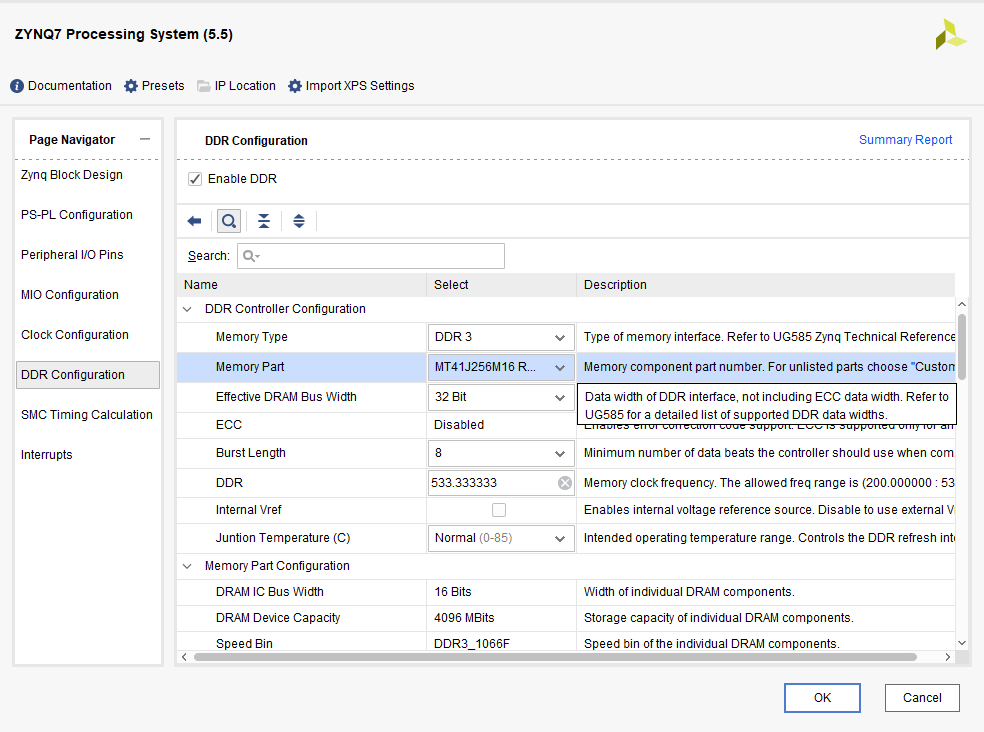

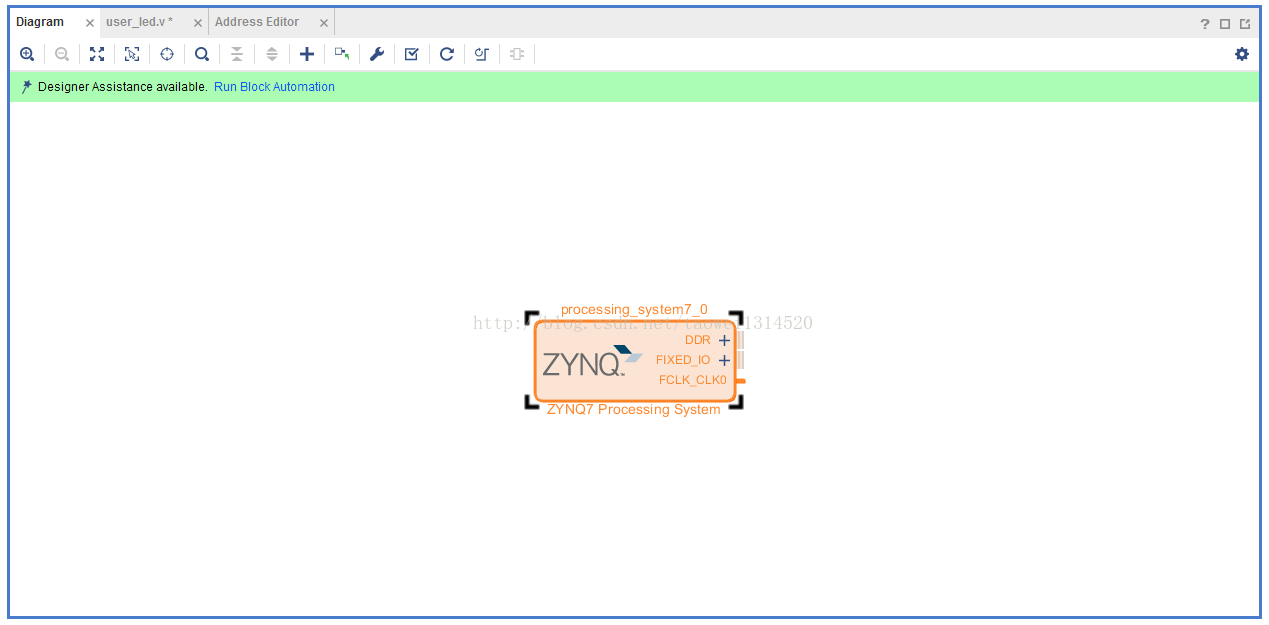

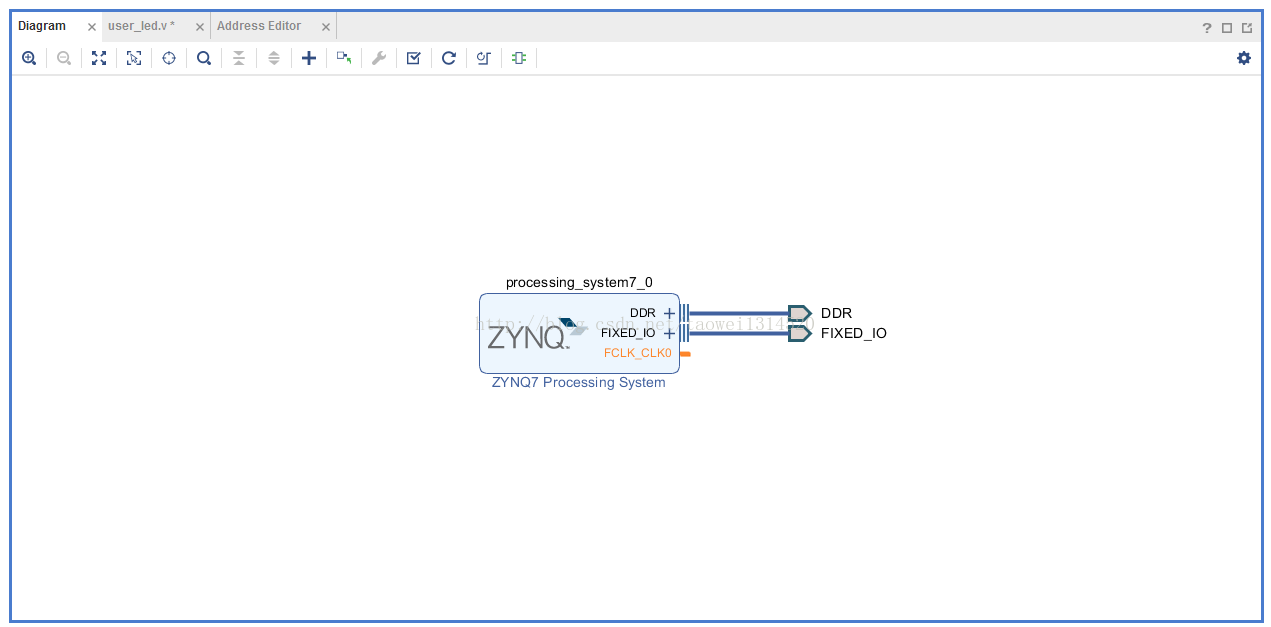

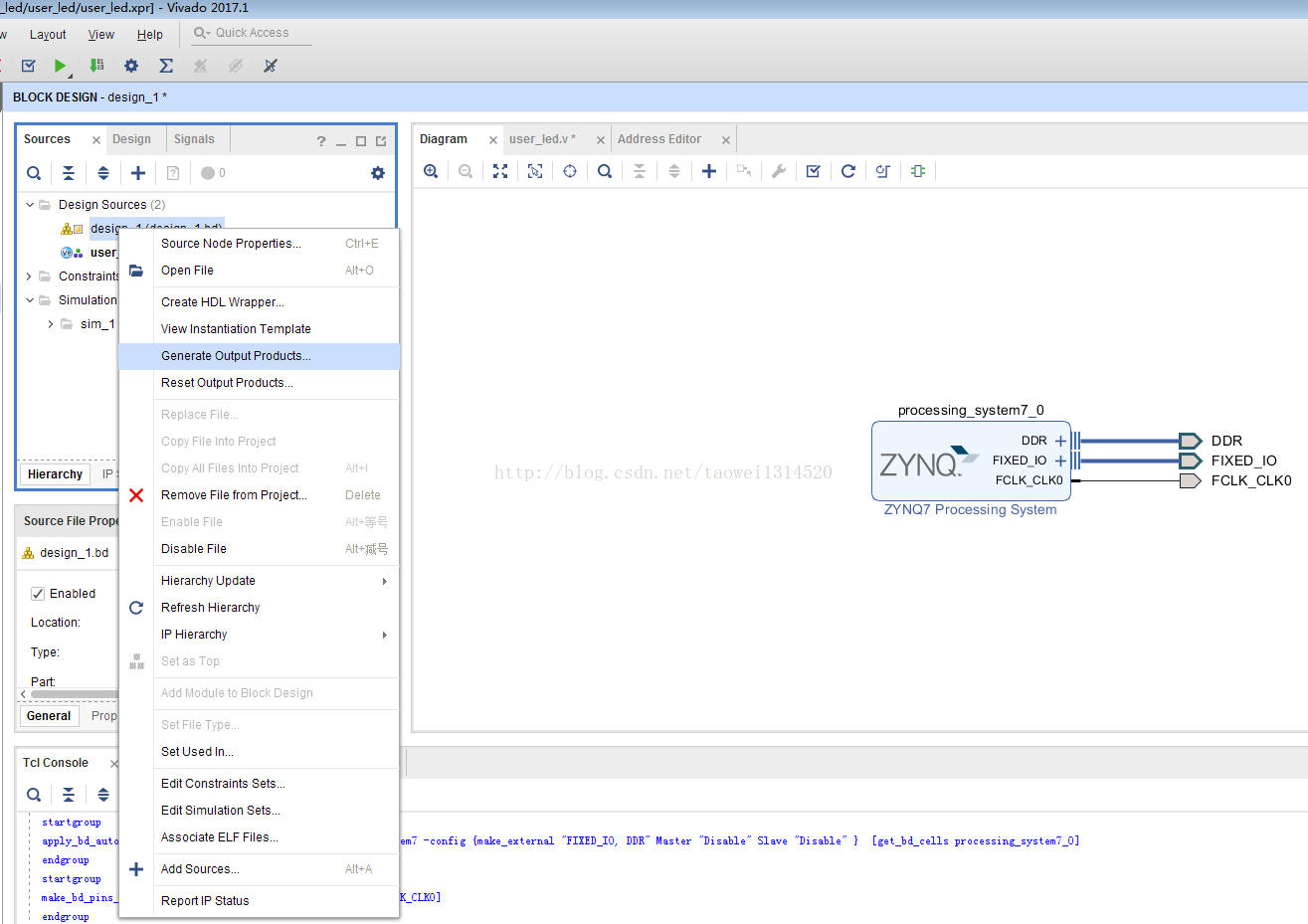

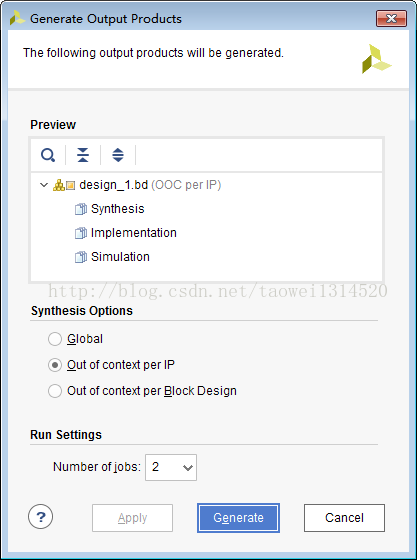

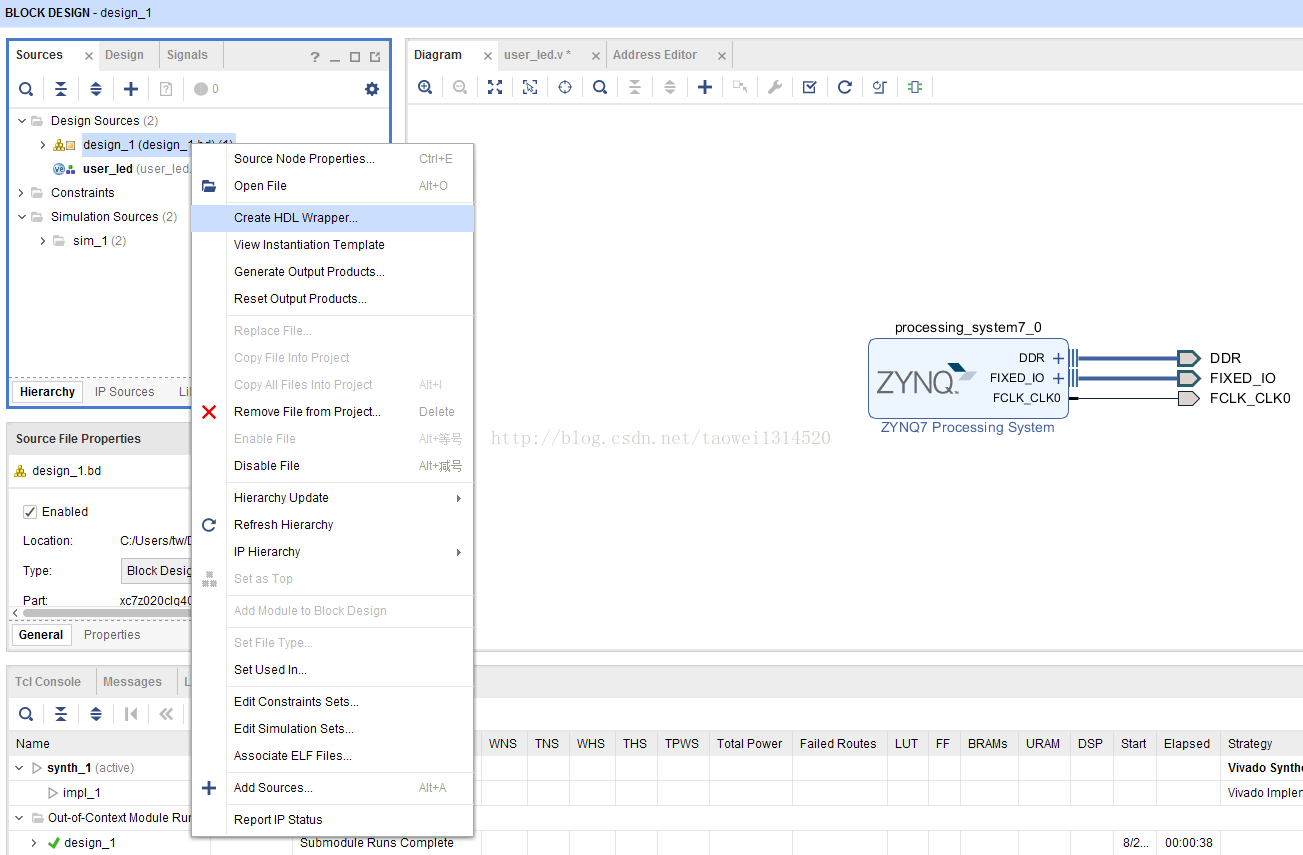

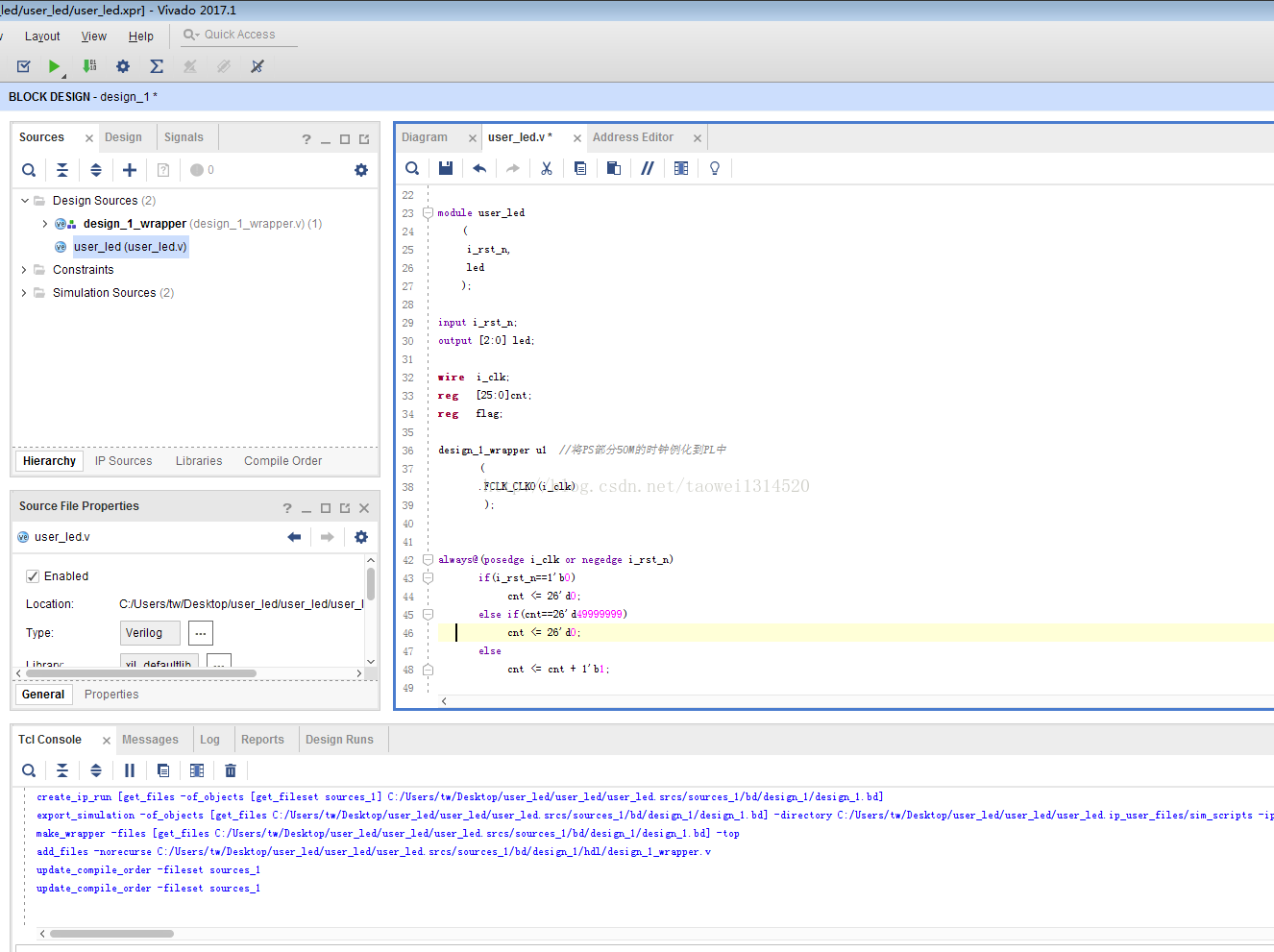

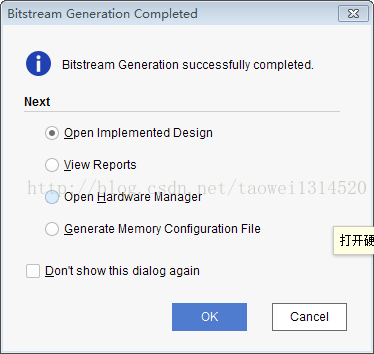

Step2 点击Flow Navigator 下的Create Block Desion新建一个Block Desion  点击OK。  Step3 点击工作区的Add IP添加IP核,在搜索栏中输入zynq 双击搜索到的ZYNQ核添加工作区内。  已经添加好的ZYNQ IP核如下图所示:  双击ZYNQ,根据需要,主要修改复位功能和AXI总线取消:  Peripheral I/O Pins根据需要勾选:  时钟勾选并配置输出50M:  选择对应的DDR型号:  ZYNQ核配置完成后如下图所示,然后点击Run Block Automation进行自动布线。  自动布线后如下图所示:  再在FCLK_CLK0上右击-->Make Ecternal将FCLK管脚引出来。  Step4 右击 design_1->Generate Ouput Products 生成综合文件。  在弹出的对话框中点击Generate:  Step5 右击 design_1->Create HDL Wrapper 生成顶层文件  在弹出的对话框中点击OK  将我们生成的ZYNQ核的顶层文件里的时钟FCLK例化到FPGA中如下图所示  Step6 新建一个XDC文件将我提供的工程里面的xdc文件复制到这个工程里

set_property PACKAGE_PIN R14 [get_ports {led[0]}]

set_property PACKAGE_PIN Y16 [get_ports {led[1]}]

set_property PACKAGE_PIN Y17 [get_ports {led[2]}]

set_property PACKAGE_PIN T11 [get_ports i_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports i_rst_n]

Step7 点击Generate Bitstream产生bit文件  生成bit文件成功后,打开硬件管理器,下载bit文件即可。 |