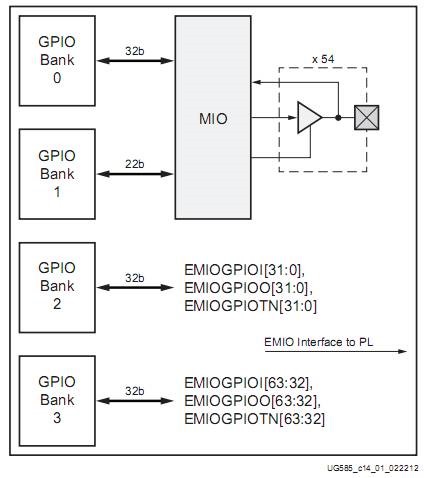

PS GPIO介绍Zynq7000系列芯片有54个MIO(multiuse I/O),它们分配在 GPIO 的Bank0 和Bank1隶属于PS部分,这些IO与PS直接相连。不需要添加引脚约束,MIO信号对PL部分是透明的,不可见。所以对MIO的操作可以看作是纯PS的操作。

GPIO的控制和状态寄存器基地址为:0xE000_A000,我们SDK下软件操作底层都是对于内存地址空间的操作

Bank0:MIO[31:0]

Bank1:MIO[52:53]

Bank2:EMIO[31:0]

Bank3:EMIO[63:32]

PS部分的GPIO有两种,MIO分配在bank0和bank1直接与PS部分相连,EMIO分配在bank2和接和PL部分相连。除了bank1是22-bit之外,其他的bank都是32-bit。所以MIO有53个引脚可供我们使用,而EMIO有64个引脚可供我们使用。

使用EMIO的好处就,当MIO不够用时,PS可以通过驱动EMIO控制PL部分的引脚。EMIO使用需要PS+PL,所以需要配合约束使用。

ZYNQ 核配置1 新建工程2 配置PLstep1: 单击Create Block Design,创建

step2: 添加ZYNQ IP

step3: 双击ZYNQ CPU IP,修改内存型号等配置

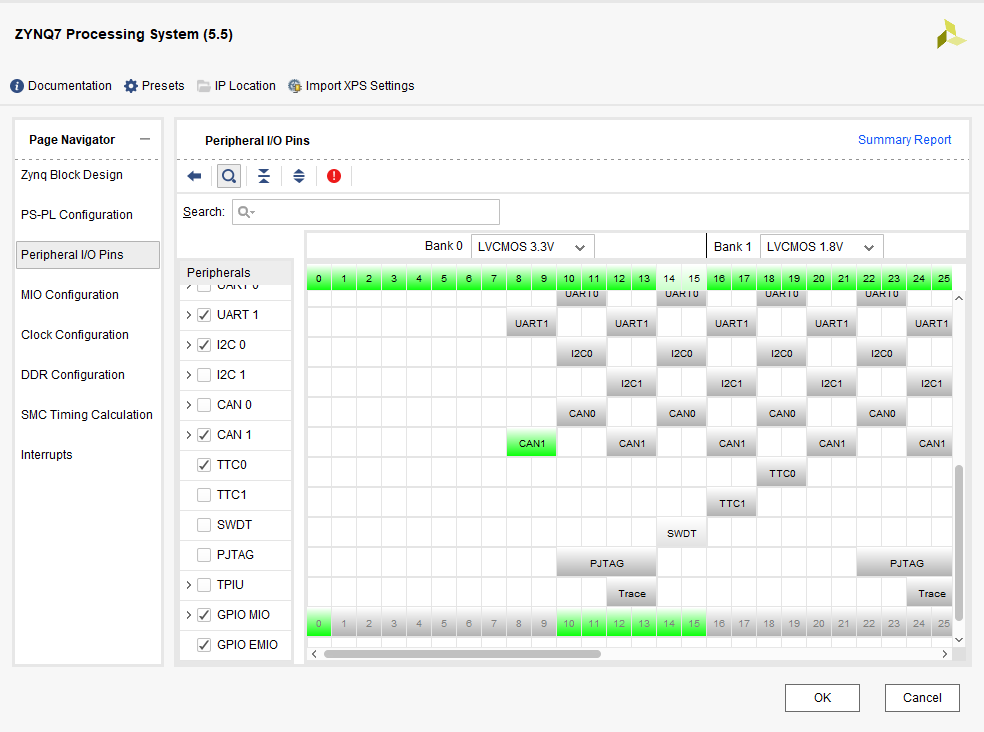

step4: 在Peripheral I/O Pins中选择GPIO复用功能,未被复用的默认GPIO功能。

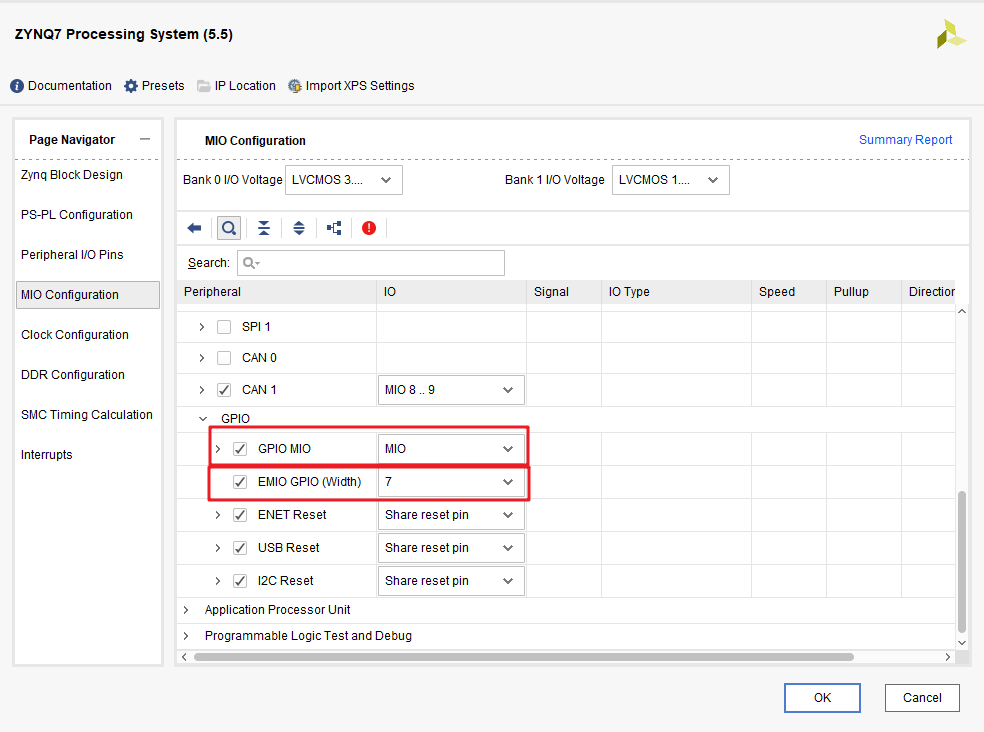

step5: 在MIO Configuration中,可以选择查看MIO的配置,可以选择EMIO数量。

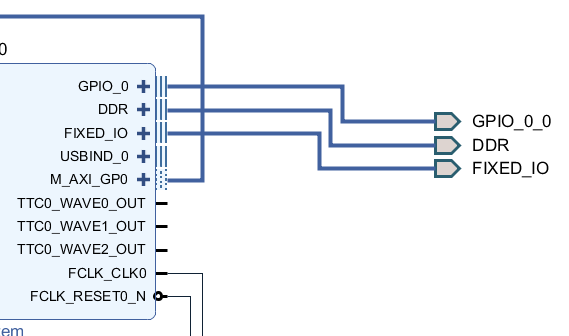

step6: 配置其他功能后,生成DHL Wrapper。相比之前的工程,多出GPIO_0_0引脚。

step7: 添加约束,wrapper文件中对应的添加对应的PL端引脚。编译生成bitstream。

3 PS配置导出硬件,打开SDK。MIO和EMIO使用步骤:

MIO初始化->配置输出方向->配置使能->控制输入/输出

以MIO7输出为例,代码如下:

#include "xgpiops.h"

#include "sleep.h"

int main()

{

static XGpioPs psGpioInstancePtr;

XGpioPs_Config* GpioConfigPtr;

int iPinNumber= 7; //LD9连接的是MIO7

u32 uPinDirection = 0x1; //1表示输出,0表示输入

int xStatus;

//--MIO的初始化

GpioConfigPtr = XGpioPs_LookupConfig(XPAR_PS7_GPIO_0_DEVICE_ID);

if(GpioConfigPtr == NULL)

return XST_FAILURE;

xStatus = XGpioPs_CfgInitialize(&psGpioInstancePtr,GpioConfigPtr, GpioConfigPtr->BaseAddr);

if(XST_SUCCESS != xStatus)

print(" PS GPIO INIT FAILED ");

//--MIO的输入输出操作

XGpioPs_SetDirectionPin(&psGpioInstancePtr, iPinNumber,uPinDirection);//配置MIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, iPinNumber,1);//配置MIO的第7位输出

while(1)

{

XGpioPs_WritePin(&psGpioInstancePtr, iPinNumber, 1);//点亮MIO的第7位输出1

sleep(1); //延时

XGpioPs_WritePin(&psGpioInstancePtr, iPinNumber, 0);//熄灭MIO的第7位输出0

sleep(1); //延时

}

return 0;

}

如果是EMIO0,iPinNumber需要改为54。

因为MIO和EMIO是同一编号的MIO共54个,从0~53。而从54开始就开始是EMIO了的范围了。之前我们应出了7个引脚gpio_0_0_tri_io[0]~gpio_0_0_tri_io[6],他们其实就依次对应54~60这几个序号,同时也对应了我们开发板上的8个LED(这是引脚约束的结果)。

下载后可以看到相应的效果。

|